- English

- Español

- Português

- русский

- Français

- 日本語

- Deutsch

- tiếng Việt

- Italiano

- Nederlands

- ภาษาไทย

- Polski

- 한국어

- Svenska

- magyar

- Malay

- বাংলা ভাষার

- Dansk

- Suomi

- हिन्दी

- Pilipino

- Türkçe

- Gaeilge

- العربية

- Indonesia

- Norsk

- تمل

- český

- ελληνικά

- український

- Javanese

- فارسی

- தமிழ்

- తెలుగు

- नेपाली

- Burmese

- български

- ລາວ

- Latine

- Қазақша

- Euskal

- Azərbaycan

- Slovenský jazyk

- Македонски

- Lietuvos

- Eesti Keel

- Română

- Slovenski

- मराठी

- Srpski језик

Епітаксійні шари: основа сучасних напівпровідникових пристроїв

Малюнок 1: Ілюструє кореляцію між концентраціями легування, товщиною шару та напругою пробою для однополярних пристроїв.

Підготовка епітаксійних шарів SiC насамперед охоплює такі методи, як вирощування випаровуванням, рідкофазова епітаксія (LPE), молекулярно-променева епітаксія (MBE) і хімічне осадження з парової фази (CVD), причому CVD є переважаючим методом масового виробництва на заводах.

Таблиця 1: надає порівняльний огляд основних методів підготовки епітаксійного шару.

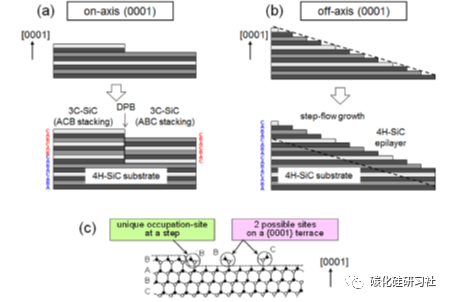

Новаторський підхід передбачає вирощування на позаосьових {0001} субстратах під певним кутом нахилу, як показано на малюнку 2(b). Цей метод значно збільшує щільність кроків, одночасно зменшуючи розмір кроків, сприяючи зародженню головним чином у місцях групування кроків і, таким чином, дозволяючи епітаксійному шару ідеально повторювати послідовність укладання підкладки, усуваючи співіснування політипів.

Рисунок 2: Демонструє фізичний процес поетапної епітаксії в 4H-SiC.

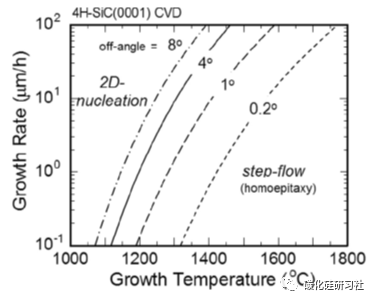

Малюнок 3: показує критичні умови для росту CVD у поетапній епітаксії для 4H-SiC.

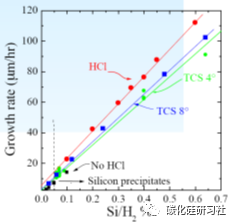

Малюнок 4: Порівняння темпів росту під різними джерелами кремнію для епітаксії 4H-SiC.

У сфері застосувань низької та середньої напруги (наприклад, пристроїв 1200 В) технологія епітаксії SiC досягла зрілої стадії, пропонуючи відносно чудову однорідність товщини, концентрації легування та розподілу дефектів, адекватно задовольняючи вимоги до SBD низької та середньої напруги. , пристрої MOS, JBS та ін.

Однак сфера високої напруги все ще створює значні проблеми. Наприклад, пристрої з номінальною напругою 10000 В вимагають епітаксійних шарів товщиною приблизно 100 мкм, але ці шари демонструють значно меншу товщину та рівномірність легування порівняно з їх низьковольтними аналогами, не кажучи вже про шкідливий вплив трикутних дефектів на загальну продуктивність пристрою. Застосування високої напруги, які, як правило, віддають перевагу біполярним пристроям, також висувають суворі вимоги до терміну служби неосновної носії, що вимагає оптимізації процесу для підвищення цього параметра.

Зараз на ринку домінують 4-дюймові та 6-дюймові епітаксіальні пластини SiC з поступовим збільшенням частки епітаксіальних пластин SiC великого діаметру. Розмір епітаксіальних пластин SiC принципово визначається розмірами підкладок SiC. Оскільки 6-дюймові підкладки SiC тепер доступні на ринку, перехід від 4-дюймової до 6-дюймової епітаксії SiC поступово триває.

У міру розвитку технології виготовлення підкладок SiC і розширення виробничих потужностей вартість підкладок SiC поступово знижується. Враховуючи, що на підкладки припадає понад 50% вартості епітаксійних пластин, очікується, що зниження цін на підкладки призведе до зниження вартості епітаксії SiC, що обіцяє світле майбутнє для галузі.**